MENU

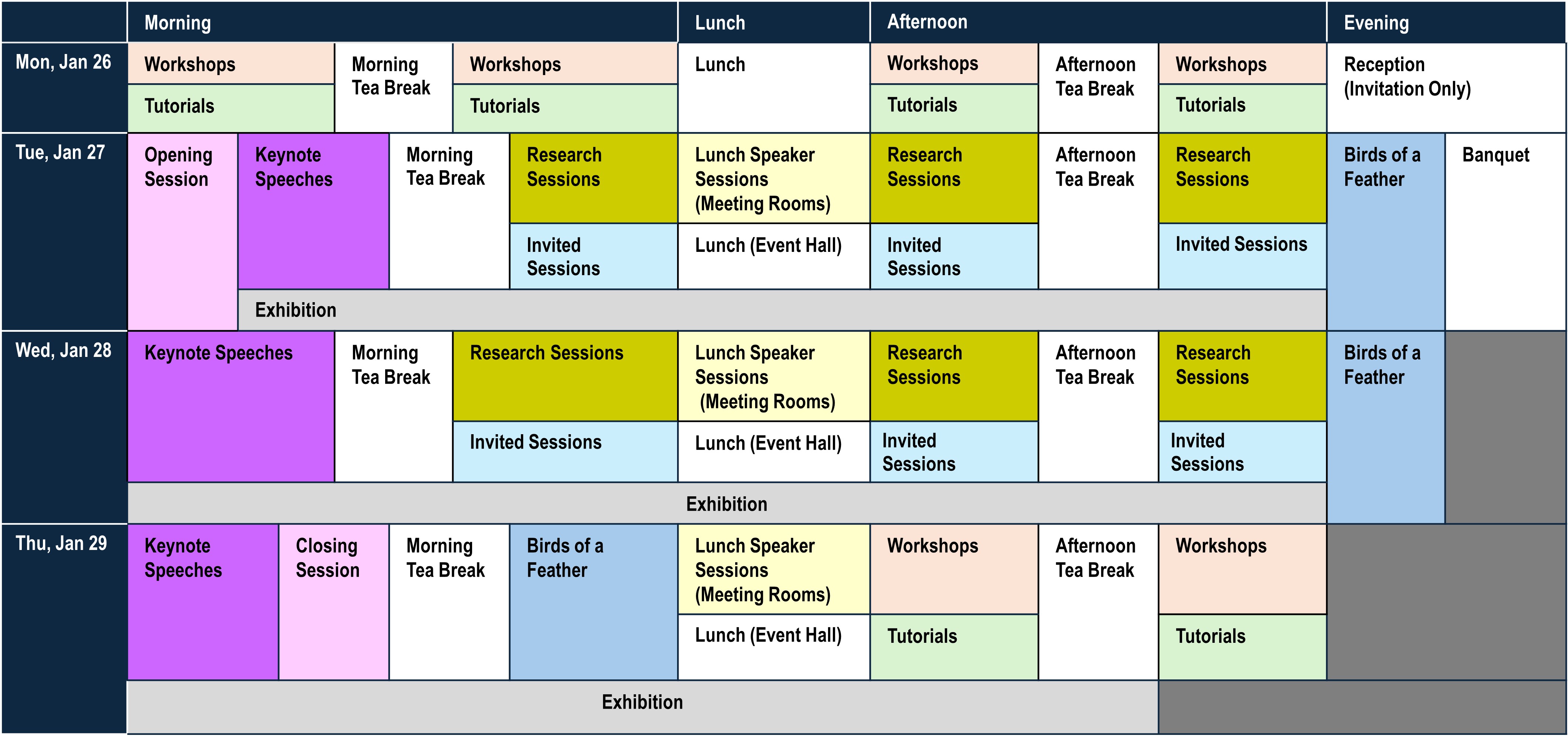

Full Program

NOTE: The program is frequently updated, and all dates, times, and room information are subject to change.

- January 26 (Mon)

- January 27 (Tue)

- January 28 (Wed)

- January 29 (Thu)

Full Day

Mon, January 26, 2026 9:30 - 16:30 Room 803

Contributors: Kazuya Yamazaki, Jack Wells, Jeff Larkin

Abstract: This workshop brings together OpenACC users from national laboratories, universities, industry, and other research institutions to exchange information and share the OpenACC programming model's uses in various science domains. A directive-based and performance-portable parallel programming model designed to program many types of accelerators, OpenACC is compatible with the C, C++, and Fortran programming languages. OpenACC simplifies the process of porting codes from host devices to various high-performance computing accelerators, significantly reducing the time and effort scientists and engineers spend programming. One may also think of OpenACC as user- specified directives that fill gaps in the standard programming languages. As standard parallel programming languages mature, one will expect that program developers will have fewer gaps to fill. This vision is consistent with greater portability and sustainability of scientific programming over time. Indeed, features pioneered in OpenACC are informing the development work of official ISO standard programming models. We are planning presentations from users of OpenACC and panel discussions of topics of interest to the community, highlighting forefront research applications in a variety of research domains and discussions of the future evolution of the OpenACC standard.

Website: OpenACC User Workshop at SCA2026

Program:

- 09:30-09:35

- Welcome and Introduction

- Kazuya Yamazaki, Jack Wells, Jeff Larkin (The University of Tokyo, NVIDIA, NVIDIA)

- 09:35-09:45

- OpenACC Specification Update

- Jeff Larkin (OpenACC Technical Chair)

- 09:45-10:20

- Compiler Updates (GCC, NVIDIA, HPE)

- Thomas Schwinge, Kazuaki Matsumura, David Oehmke (BayLibre, NVIDIA, HPE)

- 10:20-10:45

- OpenACC-based GPU acceleration for the SCALE atmospheric model: status and challenges

- Seiya Nishizawa (RIKEN)

- 10:45-11:15

- Break

- 11:15-11:35

- Optimization of the SCALE atmospheric model customized for super-parameterization

- Kazuya Yamazaki (The University of Tokyo)

- 11:35-12:05

- Governmental support for GPU-ization on HPC/AI applications toward Fugaku-NEXT and nation-wide GPU systems

- Taisuke Boku (Director, Advanced HPC-AI Research and Development Support Center, RIST / Center for Computational Sciences, University of Tsukuba)

- 12:05-12:30

- Solomon: unified schemes for directive-based GPU offloading

- Yohei Miki (The University of Tokyo)

- 12:30-13:30

- Lunch Break

- 13:30-13:55

- GPU optimization of the Japanese high-resolution atmospheric model NICAM with OpenACC

- Hisashi Yashiro (National Institute for Environmental Studies, Japan)

- 13:55-14:20

- An OpenACC-Based Implementation of Lattice H-Matrix–Vector Multiplication on GPU Clusters

- Tetsuya Hoshino (Nagoya University)

- 14:20-14:45

- GPU Acceleration and Performance Optimization of a High-Order Combustion Solver LS-FLOW-HO Using OpenACC

- Osamu Watanabe (Japan Aerospace Exploration Agency)

- 14:45-15:15

- Break

- 15:15-15:40

- Using OpenACC for Scientific Applications

- Sunita Chandrasekaran (University of Delaware)

- 15:40-16:05

- GPU-Accelerated Particle Tracing on Unstructured Meshes Using OpenACC

- Chun-Sung Jao (National Center for High-performance Computing, Taiwan)

- 16:05-16:20

- Discussions

- 16:20-16:30

- Workshop Concludes/Closing remarks

- Kazuya Yamazaki, Jack Wells, Jeff Larkin (The University of Tokyo, NVIDIA, NVIDIA)

Mon, January 26, 2026 9:30 - 16:30 12F Grand Toque

Contributors: Ikko Hamamura, Ryousei Takano, Pascal Jahan Elahi, Tommaso Macrì, Nan-yow Chen, Yun-Yuan (Pika) Wang

Abstract: The workshop *“Accelerated Quantum Supercomputing: CUDA-Q Connects HPC, Quantum, and Applications”* is a dedicated event focused on the integration of quantum computing within high-performance computing (HPC) ecosystems. Bringing together experts from HPC, quantum software, hardware, and various application domains, the program explores technical milestones and the ongoing challenges of *hybrid HPC–quantum systems*.

Key themes include distributed quantum computing, scalable architectures, and GPU simulation. The workshop balances theoretical insights with practical application, featuring a *hands-on session* with state-of-the-art quantum devices and simulators. Real-world use cases in *chemistry, optimization, and machine learning* will be showcased to demonstrate the tangible impact of quantum acceleration across scientific and industrial sectors.

By facilitating interdisciplinary dialogue, the workshop aims to *explore potential breakthroughs and discuss future directions* for scalable quantum supercomputing. Participants will gain a holistic view of the current landscape and emerging trends, fostering connections between quantum software development and HPC infrastructure. Attendees will *leave with valuable insights and practical perspectives* to contribute to the evolving field of quantum-accelerated high-performance computing.

Website: https://sites.google.com/view/sca-hpcasia2026-quantum

Program:

- 09:30-09:35

- Opening Remarks

- Ikko Hamamura (NVIDIA)

- 09:35-09:55

- ABCI-Q: Quantum-AI Hybrid Computing Information

- Ryousei Takano (AIST)

- 09:55-10:20

- Enabling GPU-Accelerated Pulse-Level QPU Emulation in Qibolab via CUDA-Q Dynamics

- Khoo Jun Yong (A*STAR)

- 10:20-10:45

- Distributed Quantum Optimization and Machine Learning in Quantum-HPC Ecosystem

- Kuan-Cheng Chen (Jij Europe/Imperial College London)

- 10:45-11:15

- Break

- 11:15-11:40

- Toward practical quantum-classical hybrid application

- Shinji Kikuchi (Fujitsu)

- 11:40-12:05

- Hybrid HPC–Quantum Workflows in Practice

- Juan Pedersen (Quantinuum)

- 12:05-12:30

- Lessons learned from real HPC+QC Integration

- Eric Mansfield (IQM)

- 12:30-13:30

- Lunch

- 13:30-14:45

- Pawsey Quantum Supercomputing Innovation Hub and Hybrid Quantum Computing

- Pascal Jahan Elahi and Tommaso Macrì (Pawsey and QuEra)

- 14:45-15:15

- Break

- 15:15-15:40

- Efficient Tensor Network Simulation of Large-Scale Quantum Circuits on HPC Systems

- Tai-Yue Li (NCHC)

- 15:40-16:05

- Recent progress in quantum algorithms for quantum chemistry

- Masaya Kohda (QunaSys)

- 16:05-16:30

- Qamomile and SQOA-QR for Sampling-Based Hybrid Quantum Optimization

- Yu Yamashiro (Jij)

Mon, January 26, 2026 9:30 - 16:30 Room 1202

Contributors: Michael Ott, Ayesha Afzal, Fumiyoshi Shoji, Natalie Bates

Abstract: As the performance, power, and heat density of supercomputers continues to grow — driven by the integration of high-power heterogeneous components such as multi-core CPUs, GPUs, high-bandwidth memory, and high bandwidth interconnects — coordinated strategies across facilities, utilities, HPC systems, and applications are required to manage energy use, reduce environmental impact, and ensure long-term operational viability.

The Energy Efficient HPC State of the Practice workshop will focus on the operational, infrastructural, and environmental challenges of deploying and managing modern high-performance computing systems. The primary objective of this workshop is to capture and disseminate best practices, case studies, and reproducible operational experiences from HPC centers, facilities, and vendors worldwide.

While energy efficiency has long been recognized as a critical constraint, sustainability metrics such as greenhouse gas (GHG) emissions, embodied carbon, and water consumption are now also coming into focus. This workshop will explore how to address these challenges across the full lifecycle of HPC systems — from design and manufacturing through daily operations, reuse, and decommissioning.

This year’s workshop also broadens its lens to consider AI infrastructure, which increasingly mirrors HPC in system architecture and operational demands. There are lessons to be learned from the HPC community that should help with the operation of Megawatt-scale AI racks, warm-water cooling, and hyperscale deployments. The convergence of these domains presents an opportunity to align practices, metrics, and innovations in service of a shared future where performance and sustainability must coexist.

Website: https://sites.google.com/lbl.gov/energy-efficient-hpc-sop-works/home

Call for Papers: https://sites.google.com/lbl.gov/energy-efficient-hpc-sop-works/call-for-papers

Program:

- 09:30-09:35

- Welcome and Introduction

- Michael Ott (LRZ)

- 09:35-10:20

- Designing and operating a sustainable Supercomputing Infrastructure: Lessons from CINES, a French National center, and the Adastra System (Keynote)

- Gabriel Hautreux (CINES)

- 10:20-10:45

- Providing Thermal Stability for an Exascale Supercomputer: A Case Study of Frontier’s Cooling System

- Grant, Martinez, Bortot, Grant, DePrater (Oak Ridge National Laboratory, Sandia National Laboratory, ENI, Queens University, Lawrence Livermore National Laboratory)

- 10:45-11:15

- Break

- 11:15-11:40

- Quantifying the Economic Potential of Energy-Aware Scheduling in HPC

- Menear, Donson, DiMont, Strelka, Clark, Slovensky (NREL)

- 11:40-12:05

- Co-Design of a Power State-Aware Scheduler and an Intelligent Power Manager for Energy-Efficient HPC Systems

- Prasasta, Pradata, Santiyuda, Amrizal, Pulungan, Takizawa (Universitas Ahmad Dahlan, Universitas Gadjah Mada, Institut Bisnis dan Teknologi Indonesia, Tohoku University)

- 12:05-12:30

- Combining System- and User-Level Approaches to Improving Energy Efficiency in GPU-Based Supercomputers

- Yoshida, Yamaki, Honda, Sato, Miwa (RIKEN R-CCS, The University of Electro-Communications)

- 12:30-13:30

- Lunch

- 13:30-13:55

- System-Level Energy Profiling of Wafer-Scale AI Systems: Characterizing Non-Accelerator Overheads in the Cerebras CS-2 System

- John, Mak, Hoffmann, Zhang, Patki, Hammer (LRZ, Cerebras Systems, LLNL)

- 13:55-14:20

- Harvesting energy consumption on European HPC systems: Sharing Experience from the CEEC project

- Kulkarni, Kemmler, Schwartz, Gedik, Chen, Papageorgiou, Kavroulakis, Iakymchuk (Friedrich-Alexander-University, University of Stuttgart, Umeå University, Aristotle University of Thessaloniki)

- 14:20-14:45

- On the Challenges of Energy-Efficiency Analysis in HPC Systems: Evaluating Synthetic Benchmarks and Gromacs

- Ravedutti Lucio Machado, Eitzinger, Hager, Wellein (Erlangen National High Performance Computing Center)

- 14:45-15:15

- Break

- 15:15-15:40

- Leveraging NVML GPM for NVIDIA GPU Monitoring

- Wassermann, Dollenbacher, Terboven, Müller (RWTH Aachen University)

- 15:40-16:25

- Panel: Operational Data Analytics

- Brandt, Frings, Shoga, Yamamoto (Sandia National Labs, Jülich Supercomputing Centre, Lawrence Livermore National Lab, RIKEN)

- 16:25-16:30

- Closing

- Natalie Bates (EE HPC WG)

Mon, January 26, 2026 9:30 - 16:30 Room 701 Room 1203

Contributors: Mehmet E. Belviranli, Seyong Lee, Keita Teranish, Ali Akoglu

Abstract: Recent trends toward the end of Dennard scaling and Moore’s law makes

the current and upcoming computing systems more specialized and complex,

consisting of more complex and heterogeneous architectures in terms of

processors, memory hierarchies, on-chip-interconnection networks,

storage, etc. This trend materialized in the mobile and embedded market,

and it is entering the enterprise, cloud computing, and high performance

computing markets.

RSDHA is a forum for researchers and engineers in both HPC domain and

embedded/mobile computing domain to gather together and discuss (1) the

latest ideas and lessons learned from the previous experience on

traditional (i.e., horizontal) and heterogeneity-based (i.e., vertical)

scaling in their own domains and (2) possible synergistic approach and

interaction between the two domains to find a good balance between

programmability and performance portability across diverse ranges of

heterogeneous systems from mobile to HPC.

Website: https://hpss.mines.edu/rsdha-26/

Call for Papers: https://hpss.mines.edu/rsdha-26/cfp.html

Program:

- 09:30-09:35

- Opening Remarks

- Keita Teranishi (Oak Ridge National Laboratory)

- 09:35-10:45

- [Keynote 1] Programming models for HPC-GPU-QPU hybrid computing

- Mitsuhisa Sato(RIKEN)

- 10:45-11:15

- Break

- 11:15-12:30

- Panel Session

- Jaejin Lee (Seoul National University), Kentaro Sano (RIKEN), Franz Franchetti (Carnegie Mellon University), Ryohei KOBAYASHI (Institute of Science Tokyo)

- 12:30-13:30

- Lunch

- 13:30-14:08

- [Paper Presentation 1] Distributed Runtime Support for Portable and Scalable Execution of Heterogeneous Applications

- Furkan Ozdemir and Ismail Akturk (Ozyegin University)

- 14:08-14:45

- [Paper Presentation 2] Adaptive Approximation-Aware Scheduling for Heterogeneous Computing Using Reinforcement Learning

- Ezgi Nur Alisan and Ismail Akturk (Ozyegin University)

- 14:45-15:15

- Break

- 15:15-16:25

- [Keynote 2] Exploring the Alternative Computing Landscape: Post-Turing Paradigms for Next-Generation HPC

- Omri Wolf (LightSolver)

- 16:25-16:30

- Closing Remarks

- Keita Teranishi (Oak Ridge National Laboratory)

This session has been cancelled due to unavoidable circumstances.

Mon, January 26, 2026 9:30 - 16:30 Room 802

Contributors: Benoit Martin, Jacques Morice, Julian Auriac, and Yushan Wang

Abstract: As HPC simulations scale toward exascale, I/O becomes a critical bottleneck due to the growing disparity between compute performance and storage bandwidth. Traditional post-hoc output models struggle with the volume and velocity of generated data. The Parallel Data Interface (PDI) offers a lightweight and flexible solution by decoupling I/O, filtering, and analysis logic from the simulation code. Through a declarative configuration system and a plugin-based architecture, PDI enables simulation developers to expose data buffers and trigger events without embedding I/O decisions directly into their application. PDI offers a simple API in C/C++, Fortran, and Python.

This full-day tutorial introduces PDI and its ecosystem of plugins: sequential and parallel HDF5 for file output, user-code and pycall for in-process custom logic execution, DEISA for in situ analytics, and Catalyst for live ParaView-based visualization. Through a combination of theoretical lectures and hands-on exercises, participants will learn how to instrument a simulation code with PDI, configure it declaratively via YAML, and drive complex I/O and visualization workflows without modifying the simulation itself.

Attendees will leave with a practical understanding of how to adopt PDI in their own projects to create modular data workflows suited for HPC.

Website: https://pdi.dev/hpcasia26

Mon, January 26, 2026 9:30 - 16:30 Room 804

Contributors: Christian Trott and Damien Lebrun-Grandié

Abstract: This tutorial provides a introduction to Kokkos, a C++ programming model designed for application performance portability across diverse computing architectures. As modern high-performance computing (HPC) increasingly relies on heterogeneous systems featuring GPUs, multicore CPUs, and other accelerators, developers face the challenge of writing code that efficiently utilizes these varied hardware resources without developing and maintaining multiple variants of the software. Kokkos addresses this by offering a single-source approach, allowing users to write code once and compile it for optimal execution on a wide range of platforms. Kokkos is an Open Source project under the Linux Foundation’s “High Performance Software Foundation" (https://hpsf.io).

We'll start by exploring the fundamental concepts of Kokkos, including memory spaces and execution spaces, which are crucial for managing data placement and task execution on different devices. You'll learn about Kokkos::parallel_for for launching parallel computations and Kokkos::View for managing data arrays efficiently on various memory architectures. Through hands-on examples, we'll demonstrate how to port simple computational kernels to Kokkos, highlighting the benefits of its abstraction layers. By the end of this tutorial, beginners will have a solid foundation for developing performance-portable applications with Kokkos, enabling them to leverage the full power of modern HPC systems. No prior experience with parallel programming models like CUDA or OpenMP is required, though basic C++ knowledge is assumed.

Mon, January 26, 2026 9:30 - 16:30 Room 1009

Contributors: Anshu Dubey, David Bernholdt, and Akash Dhruv

Abstract: Producing scientific software is a challenge. The high-performance modeling and simulation community, in particular, faces the confluence of disruptive changes in computing architectures and new opportunities (and demands) for greatly improved simulation capabilities, especially through coupling physics and scales. Simultaneously, computational science and engineering (CSE), as well as other areas of science, are experiencing an increasing focus on scientific reproducibility and software quality. Large language models (LLMs), can significantly increase developer productivity through judicious off-loading of tasks. However, models can hallucinate, therefore it is important to have a good methodology to get the most benefit out of this approach.

We propose a tutorial in which attendees will learn about practices, processes, and tools to improve the productivity of those who develop CSE software, increase the sustainability of software artifacts, and enhance trustworthiness in their use. We will focus on aspects of scientific software development that are not adequately addressed by resources developed for industrial software engineering. We will additionally impart state-of-the-art approaches for using LLMs to enhance developer productivity in the context of scientific software development and maintenance. Topics include the design, test-driven development, refactoring, code translation and testing of complex scientific software systems; and conducting computational experiments with reproducibility built in.

The inclusion of LLM assistance on coding related tasks is particularly important to include in any software productivity concern given that it has the potential to change the way development is done. It is particularly challenging to get this assistance in developing research software because of limited training data. We have developed methodologies and tools for software development and translation that use LLMs. The use of these tools and methodologies for hands-on activities will be a part of this tutorial.

Website: https://bssw-tutorial.github.io/2026-01-26-hpcasia/

Mon, January 26, 2026 9:30 - 16:30 Room 801

Contributors: Cole Brower, Samuel Rodriguez, Hiroyuki Ootomo, Yevhenii Havrylko, Paweł Grabowski, Harun Bayraktar

Abstract: While libraries exist for most commonly used mathematical operations, developers often need to write custom kernels for functionality not covered by high-level APIs. A great example is "fusing" multiple operations into a single kernel, a well-established optimization strategy that reduces kernel launch overhead and can increase arithmetic intensity and minimize global memory traffic. These benefits are particularly impactful in performance-critical applications, such as attention mechanisms in large language models. Math Device Extension (MathDx) libraries were developed to enable the rapid development of such high-performance GPU kernels.

In this tutorial, we introduce the Dx ecosystem to the GPU kernel developer community, highlighting its use in both C++ and Python and how it makes it easy to write fast, portable GPU code. Python support is enabled via nvmath-python, which brings the power of Dx libraries to data scientists and research developers without sacrificing performance.

To ground these concepts in a meaningful application, we use floating-point emulation via the Ozaki-I scheme as a hands-on case study. Attendees will learn how to implement high-precision FP64 matrix multiplication on low-precision integer Tensor Cores using the cuBLASDx library and achieve near-cuBLAS performance. This will be accomplished through dedicated access to a GPU that has a very high INT8 to FP64 tensor core throughput ratio (e.g., Ada or Blackwell). Attendees must bring their own laptop and will have the opportunity to choose to do this either in C++ or in Python. This complex algorithm serves as a compelling example of how Dx libraries enable the rapid development of high-performance GPU kernels across both domains. If time permits, there will be a second exercise utilizing cuFFTDx.

Whether you’re an HPC practitioner looking to push the boundaries of performance or a developer seeking easier, more expressive GPU programming workflows, this tutorial will increase your productivity in writing high-performance GPU code.

Mon, January 26, 2026 9:30 - 16:30 Room 805

Contributors: Todd Gamblin, Gregory Becker, Alec Scott, Phil Sakievich, and Kathleen Shea

Abstract: Modern scientific software stacks rely on thousands of packages, from low-level libraries in C, C++, and Fortran to higher-level tools in Python and R. Scientists must deploy these stacks across diverse environments, from personal laptops to supercomputers, while tailoring workflows to specific tasks. Development workflows often require frequent rebuilds, debugging, and small-scale testing for rapid iteration. In contrast, preparing applications for large-scale HPC production involves performance-critical libraries (e.g., MPI, BLAS, LAPACK) and machine-specific optimizations to maximize efficiency.

Managing these varied requirements is challenging. Configuring software, resolving dependencies, and ensuring compatibility can hinder both development and deployment. Spack is an open-source package manager that simplifies building, installing, and customizing HPC software stacks. It offers a flexible dependency model, Python-based syntax for package recipes, and a repository of over 8,500 packages maintained by over 1,500 contributors. Spack is widely adopted by researchers, developers, cloud platforms, and HPC centers worldwide.

This tutorial introduces Spack's core capabilities, including installing, managing, and authoring packages, configuring environments, and deploying optimized software on HPC systems. The tutorial is divided into two halves: the first with introductory topics and the second with advanced workflows for developers, package maintainers, and facility staff. The format is interactive; presenters will work through live demos, which attendees can also work through in live cloud instances. Attendees will gain foundational skills for automating routine tasks and acquire advanced knowledge to address complex use cases with Spack.

Half Day: Morning

Mon, January 26, 2026 9:30 - 12:30 Room 1002

Contributors: Miwako Tsuji, Filippo Spiga

Abstract: This workshop aims to provide the opportunity to share the practice and experience of high-performance computing systems using the Arm architecture and their performance and applications.

The last few years have seen an explosion of 64-bit Arm-based processors targeted toward server and infrastructure workloads, often specializing in a specific domain such as HPC, cloud, and machine learning. A wide variety of Arm based processors such as Fujitsu A64FX, AWS Graviton, Microsoft Cobalt, Google Axion, Huawei Kunpeng and NVIDIA Grace, are available. More will come online in 2027.

Sharing the practice and experiences using these Arm-based processors will contribute to advancing high-performance computing technology for newly designed systems using these new emerging Arm-based processors.

In this workshop, we invite papers on the practice and experience of the Arm-based high-performance computing systems, if available, optimization and performance analysis of high-performance workloads on Arm-based processors. We welcome performance optimization studies either through access to real hardware or via simulation/emulation frameworks.

The topics include, but are not limited to:

- HPC Applications porting

- Performance Analysis, Performance Modeling & Measurement

- SVE Vectorization analysis and optimizations

- Programming Models & Systems Software

- Arm CPUs paired with Networking oir accelerators such as GPUs

- Applications of Arm technology to Artificial Intelligence and Machine Learning

- Emerging Arm-based CPU Architectures and Technologies

Website: https://iwahpce.github.io/

Call for Papers: Please see the website for details

Program:

- 09:30-09:55

- Score-P with Arm(s) around the world ...

- Christian Feld, Gregor Corbin and Brian J.N. Wylie (JSC)

- 09:55-10:20

- System Software Utilization on an ARM-Based Supercomputer: Insights from a Production-Scale System

- Yosuke Asai, Kento Sato, Keiji Yamamoto, Hitoshi Murai and Kohei Yoshida (RIKEN, The University of Electro-Communications)

- 10:20-10:45

- Cross-architecture power efficiency analysis through micro-benchmarking

- Fabio Banchelli, Filippo Mantovani and Filippo Spiga (BSC, NVIDIA)

- 10:45-11:15

- Break

- 11:15-11:40

- Solving large-scale eigen problem in quantum few-body system on massive parallel computer

- Daisuke Yoshida, Emiko Hiyama, Toshiyuki Imamura, Issaku Kanamori and Hideo Matsufuru (Tohoku University, RIKEN, KEK, SOKENDAI)

- 11:40-12:05

- Mixed precision solvers with half-precision floating point numbers for Lattice QCD on A64FX processor

- Issaku Kanamori, Hideo Matsufuru, Tatsumi Aoyama, Kazuyuki Kanaya, Yusuke Namekawa and Hidekatsu Nemura (RIKEN, KEK, SOKENDAI, The University of Tokyo, University of Tsukuba, Fukuyama University, Osaka University)

- 12:05-12:30

- Prototyping an Autotuning Framework for Program Optimization Using Exo Language

- Rin Iwai, Jens Domke, Emil Vatai and Yukinori Sato (Toyohashi University of Technology, RIKEN)

Mon, January 26, 2026 9:30 - 12:30 Room 1003 Room 702

Contributors: Neda Ebrahimi Pour, Sabine Roller, Ryoji Takaki

Abstract: The objective of this workshop is to provide a forum for the presentation and discussion of advanced numerical simulation techniques for complex multi-scale, multi-physics, coupled problems and AI enhanced simulations on high performance computing (HPC) systems.

Applications with different characteristics in parts of the computational domain can lead to unexpected performance issues. The optimum setting for one part might be contradictory to the optimum for another; the overall optimum might be non-optimal, but still a satisfactory compromise for researchers.

A variety of methodologies have been employed during the development of individual solutions, contingent upon the specific application and the underlying hardware configuration. In terms of the application, for example, machine learning algorithms have been introduced with a view to prediction purposes of simulation results. With regard to the hardware, the introduction of both homogeneous and heterogeneous cluster settings has been considered. All combinations have advantages and disadvantages, leading to the following question: how to find the optimal configuration and setting of all parameters, with respect to quality of solution vs. computational efficiency?

Call for Papers: Please see the website for details

Program:

- 9:30-9:35

- Welcoming

- Prof. Sabine Roller (DLR) & Prof. Ryoji Takaki (JAXA)

- 09:35-10:20

- Keynote: High-fidelity flow simulations using HPC solver FFVHC-ACE and parallelized Hankel dynamic mode decomposition for large-scale data

- Prof. Hiroyuki Asada (Tohoku University)

- 10:20-10:45

- Hybrid Inference Optimization for AI-Enhanced Turbulent Boundary Layer Simulation on Heterogeneous Systems

- Fabian Orland (RWTH Aachen University)

- 10:45-11:05

- Break

- 11:05-11:25

- CityScaleCast: Spatiotemporal GNN for City-Scale Weather Prediction with GraphCast-Guided Parallel Modeling and Multi-Step Forecasting in Sendai

- Xuanwen Pan (Tohoku University)

- 11:25-11:45

- Explainable AI-Guided Genetic Algorithms for Efficient Software Automatic Tuning

- Toshinobu Katayama (Tohoku University)

- 11:45-12:05

- MemMan: A Fortran and C++ Interoperable Memory Manager on Modern High-Performance Computing Platforms

- Claudius Holeksa (NORCE Research AS)

- 12:05-12:25

- Integrating Quantum and HPC: A Prototype Hybrid Implementation and Benchmark of Quantum-Selected Configuration Interaction

- Ikko Hamamura (NVIDIA Corporation)

- 12:25-12:30

- Closing Remarks

- Prof. Sabine Roller (DLR) & Prof. Ryoji Takaki (JAXA)

Mon, January 26, 2026 9:30 - 12:30 Room 702 Room 701

Contributors: Kai Watanabe, Shoichiro Tsutsui, Koji Kusunoki, Rei Nakatani

Abstract: This workshop will discuss applications of quantum computers to the field of CAE, an area expected to see broad use across industry and academia. In recent years, this field has come to be known as “QCAE,” and intensive research and development is being carried out by companies, universities, and research institutes. By leveraging quantum computing, QCAE is expected to enable high-accuracy numerical solutions for fluid simulations, large-scale structural analysis, and complex differential equations.

Aimed at participants of HPC/SCA 2026 who specialize in HPC, this workshop will guide you from the current status and basic principles of quantum computing through to cutting-edge QCAE initiatives, presented by leading experts. We expect that a basic understanding of numerical simulation—such as CAE computations using HPC and differential equations—will be sufficient to fully appreciate the content.

In addition to talks from top players in industry and academia, we are also planning informal discussions during the coffee break to enable closer and more open exchange of ideas.

Website: https://iqcae2026.github.io/homepage/en/page.html

Program:

- 09:40-10:05

- CAE in Quantum Computing: Business overview

- Tadashi Kadowaki (National Institute of Advanced Industrial Science and Technology (AIST) / DENSO CORPORATION)

- 10:05-10:30

- CAE in Quantum Computing: Technical overview

- Prof. Kosuke Mitarai (School of Engineering Science, Graduate School of Engineering Science / The University of Osaka)

- 10:30-11:00

- Break

- 11:00-11:20

- Latest Research presentation

- Prof. Shuta Kikuchi (Graduate School of Science and Technology, Keio University)

- 11:20-11:40

- Latest Research presentation

- Prof. Koichi Miyamoto (Center for Quantum Information and Quantum Biology, The University of Osaka)

- 11:40-12:00

- Latest Research presentation

- Kentaro Tanabe (Murata Manufacturing Co., Ltd., Corporate Technology & Business Development Unit, Senior Manager)

- 12:00-12:20

- Latest Research presentation

- Yuki Sato (Toyota Central R&D Labs., Inc.)

- 12:20-12:30

- Concluding Remarks

- Organizer (QunaSys, inc.)

Mon, January 26, 2026 9:30 - 12:30 Room 1101

Contributors: Antigoni Georgiadou, Tiernan Casey, Tushar Athawale

Abstract: The EPSOUQ-HPC workshop aims to close what we see as a key gap in the HPC/supercomputing technical content, i.e. a forum for deep discussion of topics at the interface of uncertainty quantification of predictive simulation and HPC. Our workshop welcomes technical contributions in all areas at the nexus of uncertainty quantification, optimization, modeling & simulation, and high-performance computing, while also targeting specific themes where these concepts are critical to technical success. In particular we are targeting digital twins, smart computing and weather simulation, and their interaction with generative AI models including language and image generation as themes where these nexus topics are of critical importance for developing, analyzing, and interpreting predictions. This year we are also expanding the UQ pillar to include research in uncertainty visualization, which is an important tool in enabling human interpretation of the outputs of probabilistic simulations.

Website: https://events.ornl.gov/epsouqhpc2025/

Program:

- 09:30-09:35

- Welcome & Introduction

- Dr. Antigoni Georgiadou (Oak Ridge National Laboratory (ORNL))

- 09:35-10:15

- Keynote presentation: “Actionable Predictions from HPC: Physics-Based +/- Artificial Intelligence”

- Dr. Peter Coveney (Univeristy College London (UCL))

- 10:15-10:45

- Speaker presentation: “Uncertainty Quantification of Frame Selection Methods for Adaptive Sampling in Molecular Dynamics”

- Dr. Vinod Jani (Center for Development of Advanced Computing, India (CDAC))

- 10:45-11:15

- Break

- 11:15-11:45

- Speaker presentation: “Compute Less, Learn More: HPC and UQ for Energy-Conscious Training”

- Dr. Sudip Seal (Oak Ridge National Laboratory (ORNL))

- 11:45-12:20

- Speaker presentation: “From Infrastructure to Reliability: QC-HPC Integration and Uncertainty-Driven Error Mitigation”

- Mr. Amir Shehata & Dr. Antigoni Georgiadou (Oak Ridge National Laboratory (ORNL))

- 12:20-12:30

- Closing remarks

Mon, January 26, 2026 9:30 - 12:30 Room 806

Contributors: Sadaf R. Alam, Maxime Martinasso, Alex Lovell-Troy, François Tessier, David Hancock, Winona Snapp-Childs

Abstract: Exascale computing initiatives are expected to enable breakthroughs for multiple scientific disciplines. Increasingly these systems may utilize cloud technologies, enabling complex and distributed workflows that can improve not only scientific productivity, but accessibility of resources to a wide range of communities. Such an integrated and seamlessly orchestrated system for supercomputing and cloud technologies is indispensable for experimental facilities that have been experiencing unprecedented data growth rates. While a subset of high performance computing (HPC) services have been available within a public cloud environments, petascale and beyond data and computing capabilities are largely provisioned within HPC data centres using traditional, bare-metal provisioning services to ensure performance, scaling and cost efficiencies. At the same time, on-demand and interactive provisioning of services that are commonplace in cloud environments, remain elusive for leading supercomputing ecosystems. This workshop aims at bringing together a group of experts and practitioners from academia, national laboratories, and industry to discuss technologies, use cases and best practices in order to set a vision and direction for leveraging high performance, extreme-scale computing and on-demand cloud ecosystems. Topics of interest include tools and technologies enabling scientists for adopting scientific applications to cloud interfaces, interoperability of HPC and cloud resource management and scheduling systems, cloud and HPC storage convergence to allow a high degree of flexibility for users and community platform developers, continuous integration/deployment approaches, reproducibility of scientific workflows in distributed environment, and best practices for enabling X-as-a-Service model at scale while maintaining a range of security constraints.

Website: https://sites.google.com/view/supercompcloud

Program:

- 09:30-9:55

- Overview of the OpenCHAMI project and Architecture

- Alex Lovell-Troy (Los Alamos National Lab)

- 09:55-10:20

- Bootstrapping and Cluster DevOps with OpenCHAMI

- Nick Jones and David Allen (Los Alamos National Lab)

- 10:20-10:45

- Resourceful and Sovereign HPC: Bristol Digital Labs and the StackHPC Slurm Appliance

- Stig Telfer (StackHPC)

- 10:45-11:15

- Break

- 11:15-11:40

- Deploying HPC and AI platforms on premise and on the Cloud

- Miguel Gila (Swiss National Supercomputing Center)

- 11:40-12:05

- RiVault: Towards self-hosted Agentic AI for Science and More

- Jens Domke (RIKEN)

- 12:05-12:30

- Automating National Federated AI Resource Access Management with AIRRPortal

- Christopher Woods (Bristol Centre for Supercomputing)

Mon, January 26, 2026 9:30 - 12:30 Room 1010

Contributors: JESUS CARRETERO, MARTIN SCHULZ, ESTELA SUAREZ

Abstract: The HPCMALL 2026 workshop will bring together researchers from diverse areas of HPC that are impacted by or actively pursuing malleability concepts, including application developers, system architects, programming model researchers, and system software researchers. In addition to high-quality, refereed publications and talks, the workshop will provide a lively discussion forum for researchers working in HPC and pursuing the concepts of and around malleability, to reflect on the advances achieved in the field since the previous editions of this workshop.

Website: https://coco-arcos.github.io/HPCMALL2026/

Call for Papers: Please see the website for details

Program:

- 09:30-09:40

- Workshop Opening.

- Martin Schultz (Technical University of Munich)

- 09:40-10:20

- Invited Keynote. "Malleable Architecture Design for the Computing Continuum: Addressing Energy, Workload, and Scale Diversity".

- Carlos J. Barrios (INSA-CITI Laboratory Lyon)

- 10:20-10:45

- On modeling knowledge graphs for representing and explaining wide-area distributed storage system.

- Dante D. Sánchez-Gallegos (University Carlos III of Madrid)

- 10:45-11:15

- Break

- 11:15-11:40

- Improving HPC Efficiency by Implementing Malleability Customisable Techniques in Radiation Transport Simulations.

- Rafael Mayo-Garcia (CIEMAT)

- 11:40-12:05

- Toward HPC Spot Jobs: On the Feasibility of Malleable Jobs on Idle Resources.

- Hervé Yviquel (Universidade Estadual de Campinas)

- 12:05-12:30

- Efficient Data Elasticity for HPC: A Malleable Ad-hoc In-memory File System for Ephemeral Data.

- Javier García-Blas (University Carlos III of Madrid)

- 12:30

- Workshop Closing.

- Martin Schultz Technical University of Munich

Mon, January 26, 2026 9:30 - 12:30 12F Conference Hall

Contributors: Makoto Taiji, Geetika Gupta

Abstract: This workshop aims to catalyze progress at the intersection of artificial intelligence and the natural sciences by highlighting the methodological challenges and opportunities that arise when applying AI techniques to domain-specific problems in life, material, physical sciences, and related fields. Despite recent successes, the integration of AI into scientific workflows remains non-trivial due to domain constraints such as limited labeled data, complex simulation-based environments, and the need for interpretability and physical consistency. The workshop provides showcase of recent successful developments of AI models for science and discussions on future directions.

Website: https://wahibium.github.io/advancing-science-through-ai/

Mon, January 26, 2026 9:30 - 12:30 Room 1201

Contributors: Nick Brown, Enrique S. Quintana-Ortí, Sandra Catalán

Abstract: The goal of this workshop is to continue building the community of RISC-V in HPC, sharing the benefits of this technology with domain scientists, tool developers, and supercomputer operators. RISC-V is an open standard Instruction Set Architecture (ISA) which enables the royalty free development of CPUs and a common software ecosystem to be shared across them. Following this community driven ISA standard, a very diverse set of CPUs have been, and continue to be, developed which are suited to a range of workloads. Whilst RISC-V has become very popular already in some fields, and in 2022 the ten billionth RISC-V core was shipped, to date it has yet to gain traction in HPC.

Website: https://riscv.epcc.ed.ac.uk/community/workshops/hpcasia26-workshop/

Program:

- 09:30-09:35

- Introduction

- Sandra Catalán (Universitat Jaume I)

- 09:35-10:25

- Invited talk

- Erich Focht (OpenChip)

- 10:25-10:45

- Porting and Evaluation of Lustre on a RISC-V Cluster for HPC Storage Infrastructure

- Surendra Billa (Centre for Development of Advanced Computing (C-DAC))

- 10:45-11:15

- Break

- 11:15-11:40

- Migration of Ginkgo's Jacobi-Preconditioned CG Solver to Vector RISC-V

- Enrique S. Quintana-Ortí (Universitat Politècnica de València)

- 11:40-12:05

- NIMA-STEP: A Hardware-Software Co-Design Approach for Accelerating Cellular Automata Computation

- Nima Sahraneshinsamani (Universitat Jaume I)

- 12:05-12:30

- An analysis of memory access patterns in RISC-V vector workloads on heterogeneous memory architectures

- Ryo Yokoyama (Graduate School of Information Sciences, Tohoku University)

Mon, January 26, 2026 09:30 - 12:30 Room 1008

Contributors: Sebastian Stern, Tyler Takeshita, and Benchen Huang

Abstract: Classical Quantum Monte Carlo (QMC) methods leverage high-performance computing (HPC) resources to simulate complex quantum many-body systems. Recently, these methods have been extended to quantum computers (QC) in hopes to achieve better accuracy. At the same time, architectures are being developed that enable such hybrid workflows by integrating quantum and HPC resources often hosted at different locations.

In this tutorial, we demonstrate a solution to an exemplary quantum many-body problem integrating distributed classical and quantum computing systems in the cloud. Specifically, we build an end-to-end workflow to execute the subroutines of a QMC algorithm on cloud-based batch and quantum computing resources and estimate the ground state energy of the example problem Hamiltonian.

The tutorial introduces QMC and QC basics to the participants and enables them to utilize cloud-native HPC and QC technologies for hybrid workloads. During the tutorial, participants will get free access to temporary AWS accounts and can follow along the guided steps in the QMC workflow. All attendees leave with code examples they can use as a foundation for their own projects.

Mon, January 26, 2026 9:30 - 12:30 Room 1001

Contributors: Dhabaleswar K (DK) Panda and Benjamin Michalowicz (The Ohio State University, USA)

Abstract: High-Performance Networking technologies are generating a lot of excitement towards building next generation High-End Computing (HEC) systems for HPC and AI with GPGPUs, accelerators, and Data Center Processing Units (DPUs), and a variety of application workloads. This tutorial will provide an overview of these emerging technologies, their architectural features, current market standing, and suitability for designing HEC systems. It will start with a brief overview of IB, HSE, RoCE, and Omni-Path interconnect. An in-depth overview of the architectural features of these interconnects will be presented. It will be followed with an overview of the emerging NVLink, NVLink2, NVSwitch, EFA, Slingshot, and Tofu-D architectures. We will then present advanced features of commodity high-performance networks that enable performance and scalability. We will then provide an overview of enhanced offload-capable network adapters like DPUs/IPUs (Smart NICs), their capabilities and features. Next, an overview of software stacks for high-performance networks like OpenFabrics Verbs, LibFabrics, and UCX, comparing the performance of these stacks will be given. Next, challenges in designing MPI libraries for these interconnects, solutions and sample performance numbers will be presented.

Website:https://nowlab.cse.ohio-state.edu/tutorials/SCA-HPCAsia-2026_hpn/

Mon, January 26, 2026 9:30 - 12:30 Room 1102

Contributors: Murali Emani, Leighton Wilson, and Petro Jr Milan

Abstract: Scientific applications are increasingly adopting Artificial Intelligence (AI) techniques to advance science. The scientific community is taking advantage of specialized hardware accelerators to push the limits of scientific discovery possible with traditional processors like CPUs and GPUs as demonstrated by the winners of ACM Gordon Bell prize recipients in recent years. The AI accelerator landscape can be daunting for the broader scientific community, particularly for those who are just beginning to engage with these systems. The wide diversity in hardware architectures and software stacks makes it challenging to understand the differences between these accelerators, their capabilities, programming approaches, and performance. In this tutorial, we will cover an overview of the AI accelerators available for allocation at Argonne Leadership Computing Facility (ALCF): SambaNova, Cerebras, Graphcore, and Groq, focusing on their architectural features and software stacks, including chip and system design, memory architecture, precision handling, programming models, and software development kits (SDKs). Through hands-on exercises, attendees will gain practical experience in refactoring code and running models on these systems, focusing on use cases of pre-training and fine-tuning open-source Large Language Models (LLMs) and deploying AI inference solutions relevant to scientific contexts. Additionally, the sessions will cover the low-level HPC software stack of these accelerators using simple HPC kernels. By the end of this tutorial, participants will have a solid understanding of the key capabilities of emerging AI accelerators and their performance implications for scientific applications, equipping them with the knowledge to leverage these technologies effectively in their research endeavors.

Mon, January 26, 2026 9:30 - 12:30 Room 1007

Contributors: Matthew Treinish, Julien Gacon, and Jun Doi

Abstract: Quantum computing is an emerging technology which has the potential to solve some

problems which are intractable for even the largest traditional supercomputer. By

leveraging quantum mechanical phenomena to perform computation, it can offer

exponential speedups for certain classes of problems. In recent years strategies have

emerged for combining HPC systems with quantum computers that leverage the unique

strengths of both computational models. The combination of high-performance computing

with quantum computing opens up the possibility for quantum computers to reach their

full potential.

This tutorial aims to provide an introduction to quantum computing for attendees. It will

provide an overview of quantum information theory, how to use quantum computers, and

the typical workflow when using a quantum computer. Building off that base knowledge,

the tutorial will explore different programming patterns which are compatible with typical

HPC workflows. It will specifically focus on using the Qiskit open source SDK and

demonstrate how you can use it to program quantum computers. This will include real-

world examples demonstrating hybrid HPC and quantum computing workflows.

Half Day: Afternoon

Mon, January 26, 2026 13:30 - 16:30 Room 1201 Room 701

Contributors: Tomohiro Ueno, Sheng Di

Abstract: In addition to traditional applications, the rise of AI and cloud computing has significantly increased the volume of data processing and communication required in high-performance computing (HPC).

Efficient data analytics and data movement across distributed and parallel environments (e.g., the Internet, inter-node networks, and system interconnects) have become critical factors in determining the performance and energy efficiency of supercomputers, data centers, and cloud platforms.

This workshop aims to address key research challenges related to big data from multiple perspectives, including data exploration, data compression, and big data systems.

To tackle these challenges, the workshop will aim to explore practical and effective approaches to data analytics and mining, big data visualization, data integration, scalable data compression, and storage/processing systems for big data.

These investigations will consider both the characteristics of large-scale data workloads and the constraints of modern hardware architectures.

In particular, the workshop will emphasize optimization strategies for big data processing, adaptive and general-purpose compression techniques, and high-performance systems designed for high-throughput, low-latency, and hardware-efficient data operations.

Website: https://sites.google.com/view/bdxcs2026/home

Call for Papers: https://drive.google.com/file/d/1DNpeDyVSZUZoMU7huAySe6yiUTBL3bEE/view?pli=1

Program:

- 13:30-13:35

- Opening

- Tomohiro Ueno (RIKEN R-CCS)

- 13:35-14:15

- Keynote 1

- Takaki Hatsui (RIKEN SPring-8 Center)

- 14:15-14:30

- Understanding LLM Checkpoint/Restore I/O Strategies and Patterns

- Mikaila Gossman, Avinash Maurya, Bogdan Nicolae, Jon Calhoun (Clemson University, Argonne National Laboratory)

- 14:30-14:45

- DeepEBC: Compressing the Pre-Trained LLMs with Error-Bounded Lossy Compression

- Jiaqi Xu, Zhaorui Zhang, Gaolin Wei, Sheng Di, Benben Liu, Xiaodong Yu, Xiaoyi Lu (Hong Kong Polytechnic University, Argonne National Laboratory, The University of Hong Kong, Stevens Institute of Technology, University of California, Merced)

- 14:45-15:15

- Break

- 15:15-15:55

- Keynote 2

- Xiaoyi Lu (University of Florida)

- 15:55-16:10

- Performance and Area Optimization of Lossless Hardware Compression of Floating-Point Data Streams

- Linyi Li, Jason Anderson, Tomohiro Ueno (University of Toronto, RIKEN)

- 16:10-16:25

- Parallelising Stream-Based Lossless Data Compression on GPUs and CPUs

- Yue Zhang, Yuki Hara, Oliver Sinnen, Shinichi Yamagiwa (University of Auckland, University of Tsukuba)

- 16:25-16:30

- Closing

- Tomohiro Ueno (RIKEN R-CCS)

This session has been cancelled due to unavoidable circumstances.

Mon, January 26, 2026 13:30 - 16:30 Room 1003

Contributors: Murali Emani, Gokcen Kestor, Dong Li

Abstract: Artificial Intelligence (AI) and Machine Learning (ML) are rapidly reshaping scientific discovery, enabling breakthroughs in climate prediction, materials design, astrophysics, drug development, and large-scale simulations. AI for Science (AI4S) seeks to accelerate innovation by integrating advanced learning methods into scientific workflows, yet key challenges persist. These include reliably and automatically applying AI/ML to complex scientific applications, incorporating domain knowledge such as physical constraints and symmetries, improving model robustness and interpretability for high-performance computing (HPC), refining foundation models for scientific use, and reducing the energy cost of large-scale training. As AI becomes increasingly central to scientific computing and influences HPC architectures and methodologies, coordinated efforts across disciplines are essential.

The AI4S workshop provides a forum for experts from academia, industry, and government to address these challenges and highlight emerging opportunities in AI-driven science. Through plenary talks, peer-reviewed papers, keynotes, and panel discussions, the workshop fosters collaboration between AI researchers, domain scientists, and HPC practitioners. Reflecting strong engagement in the supercomputing community—as demonstrated by record participation at prior events—the workshop aims to shape future AI research directions, advance integration of AI with HPC systems, and catalyze the next generation of AI-enabled scientific discoveries.

Program:

- 13:30-13:35

- Welcome

- Murali Emani (Argonne National Laboratory (ANL))

- 13:35-14:10

- Aeris: Argonne earth systems model for reliable and skillful predictions

- TBD (Argonne National Laboratory)

- 14:10-14:45

- Optimal Sparsity of Mixture-of-Experts Language Models for Reasoning Tasks

- Rio Yokota (Institute of Science, Tokyo)

- 14:45-15:15

- Break

- 15:15-15:50

- TBD

- Mohammed Wahib (RIKEN)

- 15:50-16.25

- TBD

- 16:25-16.30

- Conclusion

- Murali Emani (ANL)

Mon, January 26, 2026 13:30 - 16:30 Room 806

Contributors: Barton Fiske, Simon See, Akihiro Kishimoto

Abstract: Scientific visualization is undergoing a transformative era, driven by the explosion of data volumes, the advent of exascale computing, and the integration of artificial intelligence and machine learning. As simulations and applications of smart cities generate increasingly complex and massive datasets, the ability to analyze, interpret, and communicate these data visually is more critical than ever. Emerging trends include the use of visualization to minimize I/O bottlenecks, the development of scalable rendering techniques for handling billion-element datasets, and the growing role of interactive and immersive visualization environments for collaborative scientific and smart city discovery. Looking ahead, scientific visualization and digital twins are poised to become even more central to research and urban workflows, enabling real-time insights, supporting decision-making in smart city planning. The future of scientific visualization and digital twins lie in its ability to adapt to new computational paradigms and to empower researchers, city planners, and decision-makers with intuitive, powerful tools for exploring and understanding the unseen in smart cities.

This workshop aims to foster collaboration among visualization and digital twins experts, domain scientists, and technology developers to advance the state-of-the-art in scientific visualization and address the challenges posed by increasingly large and complex datasets in smart city applications. By sharing best practices, innovative tools, and real-world experiences, the workshop seeks to catalyze new research directions and practical solutions that enhance the accessibility and impact of visualization across urban environments. The influence of this workshop is to empower scientists and smart city stakeholders to communicate their findings more effectively and enabling real-time visualization for urban development. Ultimately, the workshop will help bridge the gap between advanced scientific computing, visualization, and smart city needs, ensuring that visualization remains a powerful force for discovery, understanding, and urban transformation.

Website: https://sites.google.com/view/svsc-workshop-scahpcasia-26

Program:

- 13:30-13:35

- Introduction and Opening Remarks

- 13:35-13:55

- Keynote – NVIDIA Blueprint for Smart City AI

- Barton Fiske (NVIDIA)

- 13:55-14:20

- Invited Talk – From CFD to Smart Visualization: Digital Twin Solutions for Urban Air Ventilation Analysis

- Kenneth Sung (Metason)

- 14:20-14:45

- Invited Talk – Visualization for Optimization of Scientific Simulations

- Takayuki Itoh (Ochanomizu University)

- 14:45-15:15

- Break

- 15:15-15:35

- Invited Talk – Visualization of Large-Scale Urban Crowd Movement for Evacuation and Safety Planning

- Kensuke Yasufuku (The University of Osaka)

- 15:35-16:00

- Invited Talk – Large-Scale Scientific Visualization using Universal Scene Description

- liff Ho (NVIDIA)

- 16:00-16:30

- Panel discussion

- Barton Fiske (NVIDIA), Jeff Adie (NVIDIA), Kenneth Sung (Metason), Takayuki Itoh (Ochanomizu University), Kensuke Yasufuku (The University of Osaka)

Mon, January 26, 2026 13:30 - 16:30 Room 1102

Contributors: Simon Garcia de Gonzalo, Mohammad Alaul Haque Monil, Norihisa Fujita

Abstract: While computing technologies have remained relatively stable for nearly two decades, new architectural features, such as specialized hardware, heterogeneous cores, deep memory hierarchies, and near-memory processing, have emerged as possible solutions to address the concerns of energy efficiency, manufacturability, and cost. However, we expect this ‘golden age’ of architectural change to lead to extreme heterogeneity and will have a major impact on software systems and applications. In this upcoming exascale and extreme heterogeneity era, it will be critical to explore new software approaches that will enable us to effectively exploit this diverse hardware to advance science, the next-generation systems with heterogeneous elements will need to accommodate complex workflows. This is mainly due to the many forms of heterogeneous accelerators (no longer just GPU accelerators) in this heterogeneous era, and the need to map different parts of an application onto elements most appropriate for that application component. In addition, this year we acknowledge the increasing need for Co-Design. This topic will explore the methodologies, challenges, and opportunities in the co-design of hardware, software, and applications to achieve optimal performance, power efficiency, and productivity in the era of extreme heterogeneity.

Website: https://ornl.github.io/events/exhet2026/

Call for Papers: Please see the website for details

Program:

- 13:30-13:40

- Opening Remarks

- Mohammad Alaul Haque Monil (Oak Ridge National Laboratory, USA)

- 13:40-13:55

- Paper Talk 1: Orchid: Towards Heterogeneous Batched Eigenvalue Solvers

- Matthew Chung (University of California, Riverside, USA)

- 13:55-14:30

- Keynote Talk: Extreme Heterogeneity on HPC/AI - What is the next stage?

- Taisuke Boku (University of Tsukuba, Japan)

- 14:30-14:45

- Paper Talk 2: Micro-Benchmarking Communications Libraries on the MI300A Compute Partitioning Modes

- Simon Garcia de Gonzalo (Sandia National Laboratories, USA)

- 14:45-15:15

- Break

- 15:15-15:30

- Paper Talk 3: DGEMM using FP64 Arithmetic Emulation and FP8 Tensor Cores with Ozaki Scheme

- Daichi Mukunoki (Nagoya University, Japan)

- 15:30-15:40

- Paper Talk 4: Q-IRIS: The Evolution of the IRIS Task-Based Runtime to Enable Classical-Quantum Workflows

- Elaine Wong (Oak Ridge National Laboratory, USA)

- 15:40-16:20

- Panel: The future of extreme heterogeneity solutions

- 16:20-16:30

- Paper Award and closing remark

Mon, January 26, 2026 13:30 - 16:30 Room 1101

Contributors: Toshihiro Hanawa

Abstract: IXPUG Workshop at HPC Asia 2026 is an open workshop on high-performance computing applications, systems, and architecture with Intel technologies. This is a half-day workshop with invited talks and contributed papers. The workshop aims to bring together software developers and technology experts to share challenges, experiences, and best-practice methods for the optimization of HPC, Machine Learning, and Data Analytics workloads. Any research aspect related to Intel HPC products is welcome to be presented in this workshop.

Website: https://www.ixpug.org/events/ixpug-hpc-asia-2026

Call for Papers: Please see the website for details

Program:

- 13:30-13:45

- Opening Remarks & Introduction of IXPUG

- Amit Ruhela (TACC)

- 13:45-14:25

- Keynote “High-Performance Mixed-Precision Sparse Matrix Solvers for Next-Generation Computational Science and Engineering"

- Takeshi Iwashita (Kyoto University)

- 14:25-14:35

- Site update (1): TACC

- Amit Ruhela (TACC)

- 14:35-14:45

- Site update (2): KAUST

- Hatem Ltaief (KAUST)

- 14:45-15:15

- Break

- 15:15-15:45

- "Large-Scale Vlasov Simulations for Astrophysics using Non-volatile Memory as Large Memory"

- Norihisa Fujita (University of Tsukuba)

- 15:45-15:55

- Site update (3): Osaka University

- Susumu Date (Osaka University)

- 15:55-16:05

- Site update (4): JCAHPC

- Toshihiro Hanawa (JCAHPC/The University of Tokyo)

- 16:05-16:30

- Invited talk: From k-mers to Kernels: High-Performance Computing for Wheat Genomes

- Hatem Ltaief (KAUST)

Mon, January 26, 2026 13:30 - 16:30 Room 702

Contributors: Jong Choi, Masaaki Kondo, Shruti Kulkarni, Seung-Hwan Lim, Tong Shu, Elaine Wong

Abstract: With the recent advancements in artificial intelligence, deep learning systems and applications have become a driving force in multiple transdisciplinary domains. This evolution has been supported by the rapid improvements of advanced processor, accelerator, memory, storage, interconnect and system architectures, including architectures based on future and emerging hardware (e.g., quantum, superconducting, photonic, neuromorphic). However, existing research is focused on hardware accelerators, deep learning systems and applications separately, but the co-design among them is largely underexplored. To develop high-performance deep learning systems on advanced accelerators, our workshop will focus on the following three important topics:

- adaptive deep learning model exploration and training for target inference devices based on customized user demands,

- joint optimization of deep learning model design with future accelerator architecture/compiler design, and

- how to leverage state-of-the-art computational functionalities from advanced accelerators for application optimization.

Website: https://shda-workshop.github.io/

Call for Papers: https://shda-workshop.github.io/html/call4papers.html

Program:

- 13:30-13:35

- Welcome to SCA/HPCAsia Workshp SHDA 2026

- Elaine Wong (Oak Ridge National Laboratory)

- 13:35-14:20

- Invited Talk: The power of Analogous computing

- John Shalf (Lawrence Berkeley National Lab)

- 14:20-14:45

- Contributed Talk: A Unidirectional Two-Compartment Neuron Circuit with On-chip STDP learning

- Shunta Furuichi (The University of Tokyo)

- 14:45-15:15

- Break

- 15:15-15:50

- Automated Approaches for Quantum Software-Hardware Co Design

- Lukas Burgholzer (Technical University of Munich, Munich Quantum Software Company)

- 15:50-16:25

- CGRA architectures for HPC and AI

- Boma A. Adhi (RIKEN)

- 16:25-16:30

- Concluding remark

- Seung-Hwan Lim (Oak Ridge National Laboratory)

Mon, January 26, 2026 13:30 - 16:30 Room 1008

Contributors: Chen Wang, Michael Brim, Jae-Seung Yeom, Michela Taufer, Ian Lumsden, Cameron Stanavige, Hariharan Devarajan, Kathryn Mohror

Abstract: As HPC applications grow in complexity and scale, I/O (Input/Output) performance remains a persistent bottleneck. Many modern workloads, including coupled simulations, AI integration, and in-situ analytics generate and consume large volumes of data that stress shared parallel file systems. This tutorial introduces practical techniques and tools to accelerate application I/O using fast, node-local storage, with a focus on two open-source solutions: UnifyFS and DYAD.

UnifyFS is a user-level file system that provides a shared namespace backed by node-local storage, enabling scalable, high-throughput I/O for write-heavy workloads. DYAD complements this by intelligently managing the data flow of dependent workflow components (e.g., simulation and analysis) to improve data locality for read-heavy workloads. Together, these systems offer a powerful approach to tackling I/O challenges without requiring major changes to application code.

This hands-on tutorial will guide participants through:

- The challenges of I/O performance at scale in HPC environments

- The design and capabilities of UnifyFS and DYAD

- How to deploy and configure these tools on HPC systems

- Integration with HPC applications (e.g., scientific simulations and AI training) and I/O libraries (e.g., MPI-IO, HDF5)

- Use cases demonstrating I/O acceleration

This tutorial is designed for a broad HPC audience - including researchers, application developers, and system engineers - who are interested in improving the performance and efficiency of I/O-bound workloads. Prior experience with UnifyFS or DYAD is not required. Attendees will leave with a deeper understanding of how to integrate node-local storage strategies into their workflows and with practical skills to apply on existing HPC systems.

Mon, January 26, 2026 13:30 - 16:30 Room 1001

Contributors: Dhabaleswar K (DK) Panda and Nawras Alnaasan (The Ohio State University, USA)

Abstract: Recent advances in Deep Learning (DL) have led to many exciting challenges and opportunities. Modern DL frameworks such as PyTorch and TensorFlow enable high-performance training, inference, and deployment for various types of Deep Neural Networks (DNNs). This tutorial provides an overview of recent trends in DL and the role of cutting-edge hardware architectures and interconnects in moving the field forward. We will also present an overview of different DNN architectures, DL frameworks, and DL Training and Inference with special focus on parallelization strategies for large models such as GPT, LLaMA, DeepSeek, and ViT. We highlight new challenges and opportunities for communication runtimes to exploit high-performance CPU/GPU architectures to efficiently support large-scale distributed training. We also highlight some of our co-design efforts to utilize MPI for large-scale DNN training on cutting-edge CPU/GPU/DPU architectures available on modern HPC clusters. Throughout the tutorial, we include several hands-on exercises to enable attendees to gain first-hand experience of running distributed DL training on a modern GPU cluster.

Website: https://nowlab.cse.ohio-state.edu/tutorials/hidl_SCAsia26/

Mon, January 26, 2026 13:30 - 16:30 Room 1002

Contributors: Yuji Iguchi, Hitoshi Murai, Todd Churchward, Kei Sasaki, and Shun Utsui

Abstract: Researchers and HPC practitioners increasingly face the challenge of maintaining consistent software environments across diverse computing resources. As scientific workflows span multiple institutions and migrate between on-premises clusters and cloud platforms, environment inconsistency leads to wasted time, reproducibility challenges, and inefficient resource utilization. RIKEN Center for Computational Science (R-CCS) and Amazon Web Services (AWS) will demonstrate how they overcame these challenges with the "Virtual Fugaku" strategy. This tutorial demonstrates how cloud infrastructure combined with containerized software environments enables researchers to develop once and run anywhere, eliminating boundaries between computing resources. Participants will first learn to build cloud-based HPC environments, then explore how portable software stacks like those in the Virtual Fugaku project maintain consistency across diverse infrastructures.

Through lectures and hands-on labs, participants will gain understanding of both cloud HPC deployment and workload portability while maintaining performance. The tutorial explores practical approaches for building infrastructure and running consistent workloads across different environments.

Participants will apply learning through two hands-on labs: building a cloud-based HPC

cluster, then deploying portable, containerized environments. Attendees will gain

knowledge to effectively deploy and optimize portable HPC workloads across diverse

computing resources.

Mon, January 26, 2026 13:30 - 16:30 Room 1007

Contributors: Munetaka Ohtani, Shweta Salaria, and Yoonho Park

Abstract: Quantum computing has the potential to elevate heterogeneous high-performance computers to tackle problems that are intractable for purely classical supercomputers. Integrating quantum processing units (QPUs) into a heterogeneous compute infrastructure, referred to as the quantum-centric supercomputing (QCSC) model, involves CPUs, GPUs, and other specialized accelerators (AIUs, etc.). Achieving this requires collaboration across multiple industries to align efforts in integrating hardware and software.

IBM and our HPC/Quantum partners have developed software components to enable the handling of QPU workloads within the Slurm workload manager in HPC environments. This tutorial session will provide a comprehensive overview of the architecture, demonstrate how to create Slurm jobs for executing quantum workloads, and discuss the execution of Quantum-Classical hybrid workloads. Participants will gain hands-on experience though live demonstrations, exploring the integration of quantum workloads into existing HPC systems.

Efficient scheduling is only part of the solution. In the second half of the session, we will address the orchestration challenges unique to hybrid Quantum-Classical workloads—such as iterative execution, hyperparameter tuning, and backend instability. Participants will learn how to build scalable, fault-tolerant pipelines using Python-based workflow tools like Prefect. Key features such as checkpointing, automatic retries, and real-time observability will be demonstrated live, equipping attendees with the skills to manage complex quantum workloads and prepare for future challenges in scalability and reproducibility.

Tue, January 27, 2026 09:00 - 09:30 5F Main Hall

Tue, January 27, 2026 9:30 - 17:00

Wed, January 28, 2026 9:00 - 17:00

Thu, January 29, 2026 9:00 - 15:30

Venue: 3F Event Hall

Exhibitor List:

Nearly 100 exhibitors will showcase their latest technologies, products, and research results. Please see the exhibitor list and floor map below.

Exhibitor List and Floor Plan (PDF)

Exhibitors Forum:

During the exhibition hours, exhibitors will deliver 15-minute presentations. Please see the detailed program below.

Exhibitors Forum

Tue, January 27, 2026 09:30 - 10:15 5F Main Hall

Session Chair: Rio Yokota (Institute of Science Tokyo/RIKEN)

Speaker

- Torsten Hoefler

- Professor

ETH Zurich, Switzerland

Biography

Torsten Hoefler is a Professor of Computer Science at ETH Zurich, a member of Academia Europaea, and a Fellow of the ACM, IEEE, and ELLIS. He received the 2024 ACM Prize in Computing, one of the highest honors in the field. Following a Performance as a Science vision, he combines mathematical models of architectures and applications to design optimized computing systems. Before joining ETH Zurich, he led the performance modeling and simulation efforts for the first sustained Petascale supercomputer, Blue Waters, at the University of Illinois at Urbana-Champaign. He is also a key contributor to the Message Passing Interface (MPI) standard where he chaired the "Collective Operations and Topologies" working group. Torsten won best paper awards at his field's top conference ACM/IEEE Supercomputing in 2010, 2013, 2014, 2019, 2022, 2023, 2024, and at other international conferences. He has published numerous peer-reviewed scientific articles and authored chapters of the MPI-2.2 and MPI-3.0 standards. For his work, Torsten received the IEEE CS Sidney Fernbach Memorial Award in 2022, the ACM Gordon Bell Prize in 2019, Germany's Max Planck-Humboldt Medal, the ISC Jack Dongarra award, the IEEE TCSC Award of Excellence (MCR), ETH Zurich's Latsis Prize, the SIAM SIAG/Supercomputing Junior Scientist Prize, the IEEE TCSC Young Achievers in Scalable Computing Award, and the BenchCouncil Rising Star Award. Following his Ph.D., he received the 2014 Young Alumni Award and the 2022 Distinguished Alumni Award of his alma mater, Indiana University. Torsten was elected to the first steering committee of ACM's SIGHPC in 2013 and he was re-elected for every term since then. He was the first European to receive many of those honors; he also received both an ERC Starting and Consolidator grant. His research interests revolve around the central topic of performance-centric system design and include scalable networks, parallel programming techniques, and performance modeling for large-scale simulations and artificial intelligence systems. Additional information about Torsten can be found on his homepage at htor.inf.ethz.ch.

Abstract

The Ultra Ethernet Consortium set out to redefine Ethernet-based interconnects for AI and high-performance computing (HPC), culminating in the recent release of its first specification (version 1.0). This talk will analyze HPC and AI workloads with respect to their networking requirements. We will then highlight key innovations that distinguish Ultra Ethernet from existing solutions, ranging from lossy operation—both with and without trimming—to fully hardware-offloaded rendezvous protocols. We will explore the architectural advancements and technical highlights that enhance efficiency, scalability, and performance, positioning Ultra Ethernet as a transformative force in next-generation computing.

Tue, January 27, 2026 10:15 - 11:00 5F Main Hall

Session Chair: Kengo Nakajima (University of Tokyo/RIKEN)

Speaker

- Keisuke Fujii

- Distinguished Professor

The University of Osaka, Japan

Biography

Keisuke Fujii is a Distinguished Professor at the Graduate School of Engineering Science, Osaka University, where he also serves as Deputy Director of the Center for Quantum Information and Quantum Biology (QIQB). He concurrently leads a research team at the RIKEN Center for Quantum Computing and acts as Chief Technical Advisor at QunaSys Inc., a leading quantum computing software start-up in Japan. He received his Ph.D. in Engineering from Kyoto University in 2011, and has held academic positions at the University of Tokyo and Kyoto University before joining Osaka University in 2019.

Professor Fujii’s research spans a broad spectrum of quantum information science, with a primary focus on the theory of fault-tolerant quantum computation, quantum error correction, quantum algorithms. His achievements have been recognized with the NISTEP Award (2020), the JSPS Prize (2022), and the Osaka University Distinguished Professor title (2022).

Abstract

The past decade has witnessed remarkable progress in the development of quantum computers, culminating in the current era of noisy intermediate-scale quantum (NISQ) devices. While NISQ hardware has enabled first demonstrations of quantum advantage in carefully chosen tasks, its limited qubit number and error rates severely restrict practical applications. Bridging the gap toward fault-tolerant quantum computing (FTQC) requires both architectural innovation and resource-efficient error correction strategies. In this talk, I will provide an overview of the state of the art, highlighting how recent advances in algorithms, quantum error correction, and partially fault-tolerant architectures can pave the way for scalable computation. I will discuss how algorithm design and resource estimation are evolving hand in hand with hardware progress, shaping a roadmap from proof-of-principle demonstrations to early fault-tolerant applications. Special emphasis will be placed on the notion of “early FTQC,” which seeks to exploit partial fault tolerance to reduce overhead while delivering meaningful computational power. By connecting theoretical advances with experimental milestones, I aim to illustrate how high-performance quantum computing may emerge in the future and outline the key challenges and opportunities that lie ahead on the path from NISQ to FTQC.

Tue, January 27, 2026 11:30 - 12:30 Room 1003

Contributors: Addison Snell (Intersect360 Research)

Abstract: In this fast-paced panel format, Addison Snell invites four panelists – two from HPC and AI-using sites (ideally one lab, one industrial) and to from the vendor community (possibly SCA / HPC Asia sponsors) to play the role of the industry analyst by responding to forward-looking questions about the direction of the industry. The panel will address seven topics in 45 minutes. The audience will see the topic list and questions for the panelist on slides, with a timer, and the slides will auto-advance as the timer expires.

Panelists:

- Murali Emani, Argonne National Laboratory

- Sabine Roller, TU-Dresden

- Andrew Jones, Microsoft Azure

- Yoshihiro Kusano, Fujitsu

Tue, January 27, 2026 11:30 - 12:30 Room 702

Contributors: Eric Van Hensbergen (Arm)

Abstract: The exponential growth in compute demand from AI workloads has led to increasingly challenging infrastructure requirements. This panel brings together industry leaders to discuss how AI accelerators, compute racks, and AI clusters are evolving to address these requirements. In this panel session, panelists will highlight how future innovations in compute, accelerators, networking, optics, and cooling can enable greater compute capacity, efficiency, and performance at scale.

Speakers:

- Eric Van Hensbergen (Arm)

- Mohamed Wahib (RIKEN)

- Jay Boisseau (Google HPC)

- Jason Haga (AIST)

- Dan Ernst (Nvidia)

- Jennifer Glore (Rebellions)

Tue, January 27, 2026 11:30 - 17:00 Room 1001

Wed, January 28, 2026 11:00 - 17:00 Room 1001

Contributors: Taisuke Boku (University of Tsukuba), Andrew Rohl (National Computational Infrastructure (NCI), the Australian National University (ANU))